Moore’s Law has supported our lives for quite some time, and it is not dead yet. Chip manufacturers are striving to accelerate the miniaturization of transistors to continue this law.

Recently, a research group in China appears to have created the smallest transistors in the world.

China appears to have created the smallest transistors in the world.

Over the past few decades, scientists and engineers have been working to miniaturize transistors to the point where the smallest instances consist of just tens of atoms. Since the first integrated circuits emerged in the 1950s, the pace of progress in transistor miniaturization has followed Moore’s Law, which predicts that the density of functional components in integrated chips will double every two years.

Unfortunately, progress in this direction has slowed significantly in recent years. The main reason behind this issue is that we are rapidly approaching the physical limits of existing materials and manufacturing processes.

Graphene and carbon nanotubes are crucial in creating small transistors.

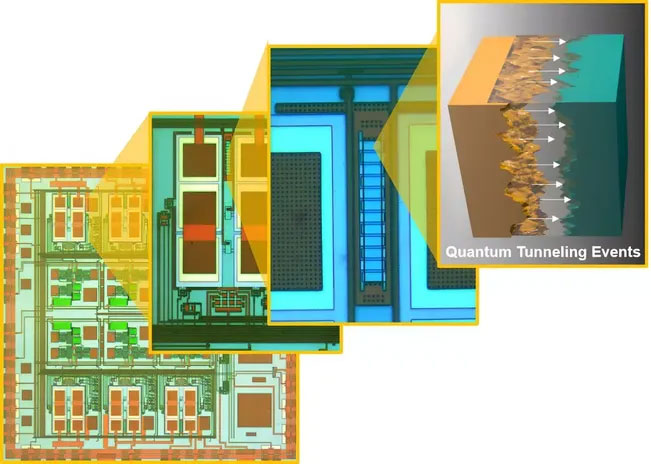

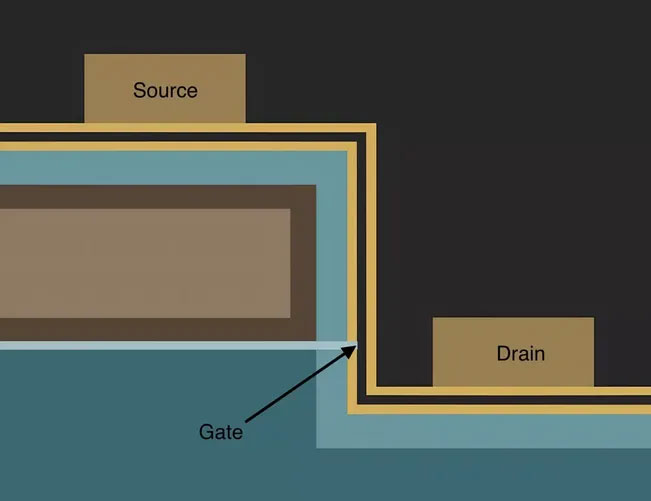

More specifically, we cannot create gate transistors, which control the flow of electricity from the source to the drain, smaller than 5nm due to a phenomenon known as quantum tunneling, which prevents them from functioning as intended.

Materials such as graphene and carbon nanotubes can be very important in creating smaller transistors due to their physical properties, but it will take some time to develop these devices.

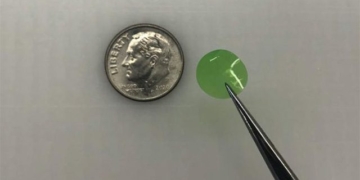

In a paper published this week, Chinese researchers claimed to have created a transistor with the smallest gate length ever reported. This significant milestone was achieved by creatively using graphene alongside molybdenum disulfide, arranging them into a two-tiered stair structure.

At the higher tier, we have the source, and at the lower tier, we have the drain. Both are made of a palladium-titanium alloy, separated by the surface of the staircase – which is made of a semiconductor material called molybdenum disulfide, itself sitting on a layer of hafnium dioxide that acts as an insulator.

This design leverages the edges of graphene sheets.

Inside the higher tier is a sandwich layer of aluminum, covered by aluminum oxide, which sits atop a graphene sheet – a single layer of carbon atoms. The aluminum oxide acts as an insulator, except for a small gap on the vertical wall of the higher tier, where the graphene sheet is allowed to contact the molybdenum disulfide. The entire staircase structure rests on a thick layer of silicon dioxide.

This design takes advantage of the edges of the graphene sheets. This means that when the gate is in the “on” state and only 0.34nm wide, it is essentially the width of the graphene layer itself. Another notable feature of this “wall transistor” is the insignificant leakage current due to the high off-state resistance.

Manufacturers may leverage these results for energy-efficient applications. Moreover, it will be relatively easy to fabricate, although many prototypes require quite a bit of voltage to operate.

Gate sizes smaller than 0.34nm are nearly impossible.

Co-author of the study, researcher Tian-Ling Ren from Tsinghua University, stated that this could be the “final breaking point for Moore’s Law.” He also believes that gate sizes smaller than 0.34nm are nearly impossible.

Of course, the researchers behind the transistor have only demonstrated that a transistor can be fabricated using a one-atom-thick material, without inventing a new process to accurately position the necessary layers. Reliable fabrication of billions of these wall transistors remains a distant dream but is a significant step towards fostering hope for faster, more efficient devices in the future.

Meanwhile, Samsung, Intel, and TSMC are working hard to make gate-all-around field-effect transistors (GAA-FET) a reality, standardizing the interconnects for chiplet designs.